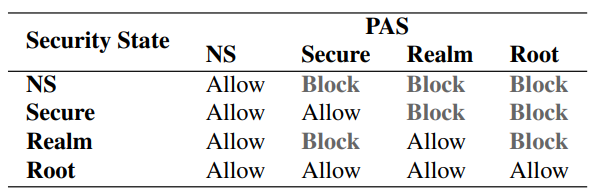

Access Control Policy of RME: In the context of the RME (Realm Management Entity) access control policy, the entity attempting to access a granule is associated with a specific security state. The Physical Address Space (PAS), on the other hand, is a characteristic that solely pertains to the granule that is being accessed.